# **Ag5700**

## Miniaturised Surface Mount 24W Power-over-Ethernet Module

#### **Features**

- 24W continuous output power, 30W peak output power (IEEE802.3at)

- > 89% efficient DC/DC converter

- > 12V and 24V variants available

- Low output ripple & noise

- Overload, short-circuit and thermal protection

- Adjustable output voltage

- > Industrial temperature range

- Minimal external components required

- Class 4 IEEE802.3 PD

- ➤ IEEE802.3bt, IEEE802.3at, IEEE802.3af compliant

- Small Surface mount (SMT) package size

- > 1500Vdc isolation (input to output)

- Silvertel "design-in" assistance

#### **Description**

The Ag5700 series Power-over-Ethernet (PoE+) modules are designed to extract power from a conventional twisted pair Category 5 Ethernet cable, conforming to the IEEE802.3 PoE standard, with full backwards compatibility with the IEEE802.3bt, IEEE802.3at and IEEE802.3af amendments.

The Ag5700 is pre-configured as a Type 2 Class 4 device, allowing the module to draw up to 30W of power from the PSE, with nominal output voltages of 12V or 24V.

The high efficiency DC/DC converter can achieve up to 89% efficiency and operates over a wide input voltage range with a low ripple and low noise output. The DC/DC converter also has built-in output overload, output short-circuit and over-temperature protection and provides a 1500Vdc (input to output) isolation barrier.

#### V1.1 December 2023

## **Table of Contents**

| 1              | 1 Product Overview                                               |                      |

|----------------|------------------------------------------------------------------|----------------------|

|                | 1.1 Ag5700 Product Selector                                      |                      |

|                | 1.2 Package Format                                               | 4                    |

|                | 1.3 Pin Description                                              |                      |

| 2              |                                                                  |                      |

|                | 2.1 Typical Connections                                          |                      |

|                | 2.2 Input                                                        |                      |

|                | 2.2.1 PD Signature                                               |                      |

|                | 2.2.2 Power Classification                                       |                      |

|                | 2.2.3 PSE Type Detection                                         |                      |

|                | 2.3 Output                                                       |                      |

|                | 2.3.1 Maximum output power                                       |                      |

|                | 2.3.2 Output Voltage Adjust Setting                              |                      |

|                | 2.3.3 Output Filtering                                           |                      |

| 3              |                                                                  |                      |

| 4              |                                                                  |                      |

| 7              | 4.1 Thermal Considerations                                       |                      |

| 5              |                                                                  |                      |

| J              | 5.1 Input Protection                                             |                      |

|                | 5.2 Output Back Feed Protection                                  |                      |

|                | 5.3 Output Short Circuit Protection                              |                      |

|                | 5.4 Thermal Protection                                           |                      |

| 6              |                                                                  |                      |

| 7              |                                                                  |                      |

| 8              |                                                                  |                      |

| 9              | 8.1 Absolute Maximum Ratings                                     |                      |

|                | 8.2 Recommended Operating Conditions                             |                      |

|                | 8.3 DC Electrical Characteristics                                | 18                   |

| 9              |                                                                  |                      |

|                | 10 Packaging                                                     |                      |

| . (            | 10 1 dottdynig                                                   | 20                   |

| _              | Table of Figures                                                 |                      |

| I              | Table of Figures                                                 |                      |

|                | Figure 1: Block Diagram                                          |                      |

|                | Figure 2: Ag5700 Package Format                                  |                      |

|                | Figure 3: Typical System Diagram                                 |                      |

|                | Figure 4: Two Event Physical Layer Detect Configuration          |                      |

|                | Figure 5: Output Voltage Adjustment                              |                      |

|                | Figure 6: Output Filter                                          |                      |

|                | Figure 7: Ag5700 Efficiency                                      |                      |

|                | Figure 8: Ag5700 operating temperature profile                   |                      |

|                | Figure 9: Thermal Relief                                         |                      |

|                | Figure 10: Thermal Interface Application Region                  | 12                   |

| Fi             |                                                                  |                      |

|                | Figure 11: Additional Heatsinking                                | 12                   |

|                | Figure 12: Input Protection                                      | 13                   |

|                |                                                                  | 13                   |

| Fi             | Figure 12: Input Protection                                      | 13<br>15             |

| Fi<br>Fi       | Figure 12: Input ProtectionFigure 13: Typical Connection Diagram | 13<br>15<br>19       |

| Fi<br>Fi<br>Fi | Figure 12: Input Protection                                      | 13<br>15<br>19<br>19 |

#### **Product Overview**

## 1.1 Ag5700 Product Selector

| Part<br>Number <sup>1</sup> | Nominal<br>Output<br>Voltage | Output Power               | Marking <sup>2</sup> | Package |

|-----------------------------|------------------------------|----------------------------|----------------------|---------|

| Ag5712LPB                   | 12V                          | 24W Continuous, 30W Peak   | ab12c                | SMT     |

| Ag5724LPB                   | 24V                          | 24vv Continuous, 30vv Peak | ab24c                | SIVII   |

Note 1: Complies with the European Directive 2011/65/EU for the Restriction of use of certain Hazardous Substances (RoHS) including Directive 2015/863 published in 2015, amending Annex II of Directive 2011/65/EU. Moisture Sensitive Level 1 and HBM 1.

Note 2: Located on the transformer.

The first letter, a, indicates the week as A-Z with uppercase being weeks 1-26, lower case weeks 27-52.

The second letter, b, indicates the year in uppercase A-Z starting from 2020. The two digits are the nominal output voltage,

The final letter, c, is a Silvertel reference.

**Table 1: Ordering Information**

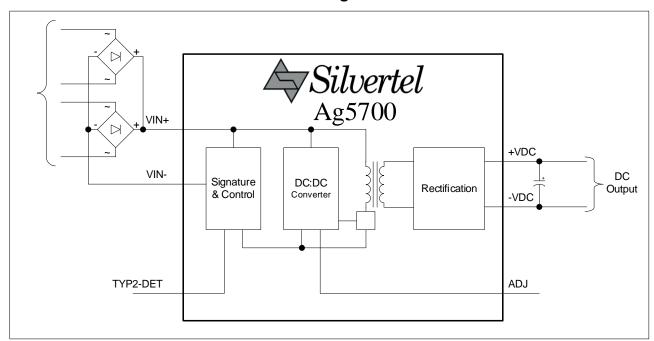

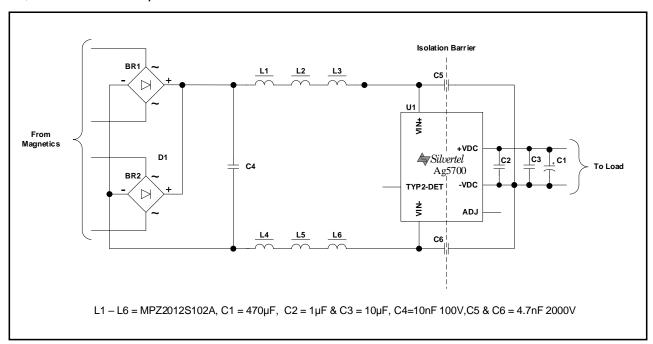

Figure 1: Block Diagram

## 1.2 Package Format

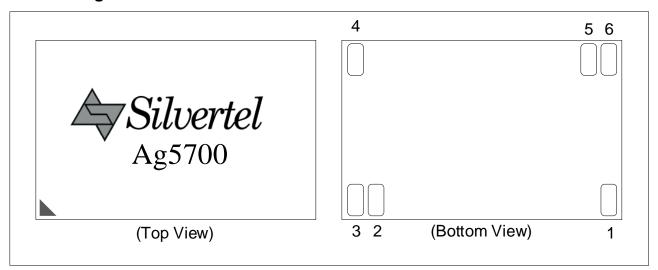

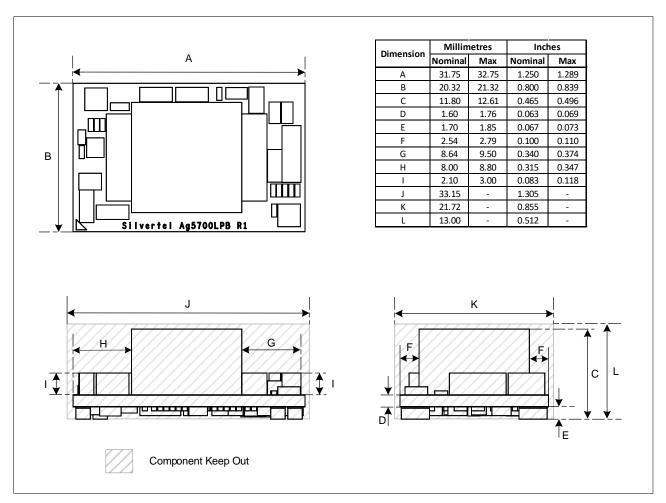

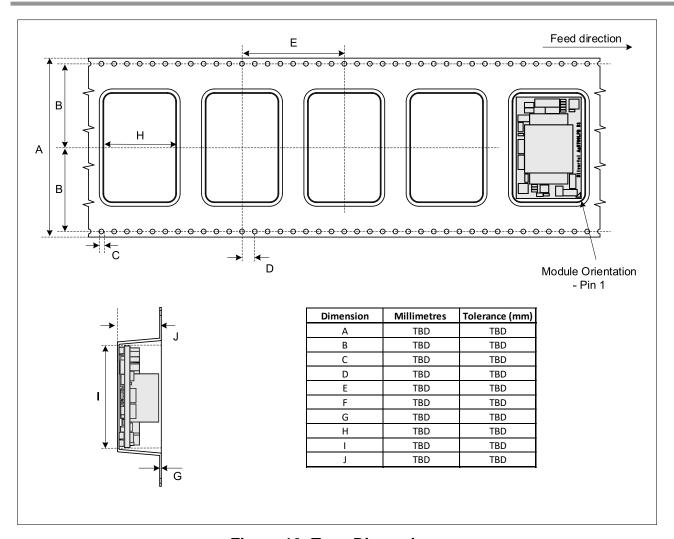

Figure 2: Ag5700 Package Format

## 1.3 Pin Description

| Pin # | Name     | Description                                                                                                                                                        |

|-------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | +VDC     | <b>Positive DC Output.</b> This pin provides the positive regulated output from the Ag5700.                                                                        |

| 2     | -VDC     | <b>Negative DC Output.</b> This pin provides the negative regulated output from the Ag5700 and is internally connected to pin 10.                                  |

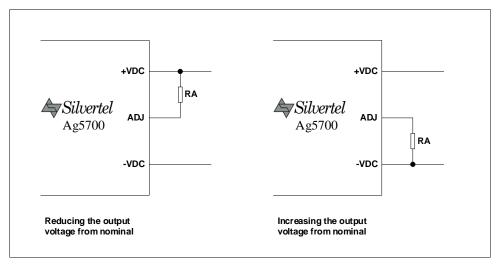

| 3     | ADJ      | Output Adjust. The output voltage can be adjusted from its nominal value, by connecting an external resistor from this pin to either the +VDC pin or the -VDC pin. |

| 4     | VIN+     | <b>POE Direct Input +</b> . This pin connects to the positive (+) output of the POE input bridge rectifiers.                                                       |

| 5     | TYP2-DET | <b>Type 2 Detect Output.</b> This pin indicates if an IEEE802.3at PSE is supplying power to the Ag5700; see Section 2.2.3 for more details.                        |

| 6     | VIN-     | <b>POE Direct Input -</b> . This pin connects to the negative (-) output of the POE input bridge rectifiers.                                                       |

**Table 2: Pin Description**

#### 2 Functional Description

#### 2.1 Typical Connections

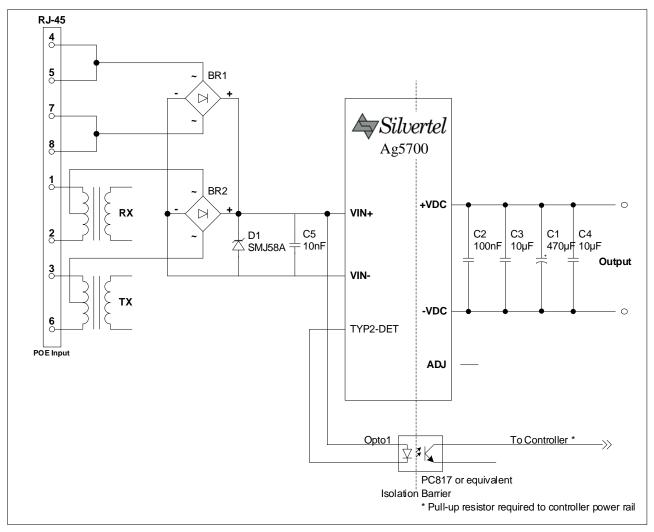

The Ag5700 only requires a few external components - the bridge rectifiers on the  $V_{IN}$  input are to conform to the input polarity protection requirement. The 470 $\mu$ F capacitor (C1) connected across the output is required for correct operation of the DC/DC converter. This capacitor must be positioned as close to the output pins as possible for optimal stability. It can be a low cost electrolytic capacitor (a minimum of 470 $\mu$ F 16V is recommended for 12V) as shown in Figure 3; it does not need to be a low ESR type for operation in temperatures down to 0°C. But if ambient temperatures below 0°C are expected, a capacitor that retains a moderately low ESR and the minimum capacitance is essential for operation. Polymer Aluminium Solid Electrolytic Capacitors are ideal for this application.

The output voltage can be adjusted by simply connecting a resistor between the ADJ pin and either the +VDC Pin or the -VDC pin, see section 2.3.2 Output Voltage Adjust Setting.

Figure 3: Typical System Diagram

#### 2.2 Input

The Ag5700 has two input pins VIN+ and VIN-, these pins should be connected to the outputs of two external bridge rectifiers (see Figure 3: Typical System Diagram). This allows the Ag5700 to be compatible with Power Sourcing Equipment (PSE) that uses the different power options (power on the Data Pair or power on the Spare Pair).

The Ag5700 is designed to be powered by any compliant IEEE802.3 PSE such as Silvertel's Ag6120.

#### 2.2.1 PD Signature

The Ag5700 complies with the IEEE802.3 specifications and provides signature and control circuitry specified within. When the inputs are connected to a PSE, they will automatically present a Powered Device (PD) signature to the PSE (when requested). The equipment will then recognise that a PD is connected to that line and supply power.

#### 2.2.2 Power Classification

The Ag5700 is a fixed Type 2 - Class 4 PD requesting 30W of power from a compliant IEEE802.3 Type 2 or greater PSE by displaying the correct class pulses shown in Table 3 below. If the Ag5700 is connected to a Type 1 PSE, the PSE will not recognise the Class 4 request from the Ag5700 and default to a Class 3 power level device and supply 15.4W.

| Туре | Requested<br>Class | Class<br>Pulse<br>A | Class<br>Pulse<br>B | PSE Output<br>Power (W) | Min. Available<br>PD Power (W) | IEEE Spec.<br>Amendment |  |

|------|--------------------|---------------------|---------------------|-------------------------|--------------------------------|-------------------------|--|

|      | 1                  | 1                   | N/A                 | 4                       | 3.84                           |                         |  |

| 1    | 2                  | 2                   | N/A                 | 7                       | 6.49                           | 802.3af                 |  |

|      | 3                  | 3                   | N/A                 | 15.4                    | 13                             |                         |  |

| 2    | 4                  | 4                   | 4                   | 30                      | 25.5                           | 802.3at                 |  |

| 3    | 5                  | 4                   | 0                   | 45                      | 40                             |                         |  |

| 3    | 6                  | 4                   | 1                   | 60                      | 51                             | 802.3bt                 |  |

| 1    | 7                  | 4                   | 2                   | 75                      | 62                             | 602.3Dt                 |  |

| 4    | 8                  | 4                   | 3                   | 90                      | 71.3                           |                         |  |

**Table 3: Classification Table**

#### 2.2.3 **PSE Type Detection**

The IEEE802.3 specification stipulates that if a device detects it is connected to a PSE that is not capable of providing the full requested power level, the device should either remain in a reduced power mode or indicate to the user that the device is under powered.

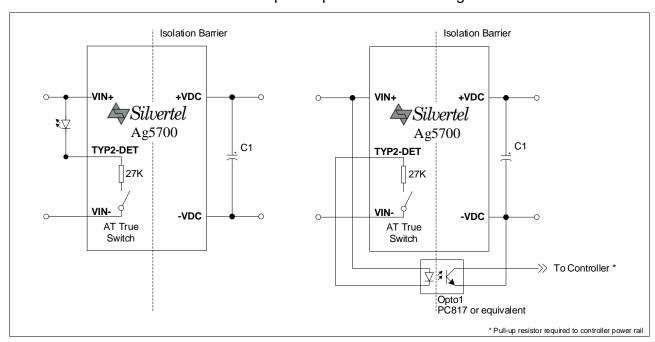

To achieve this, the Ag5700 has an output pin, TYP2-DET, to indicate that it has been connected to a PSE that can supply enough power to operate at its full power output. This pin will pull low from Vin+ once the Ag5700 has detected a two event physical layer classification, as described in the IEEE802.3at or IEEE802.3bt specification amendments, this can be used to drive an LED or Optocoupler as shown in Figure 4.

Figure 4: Two Event Physical Layer Detect Configuration.

If the Ag5700 detects a Two Event Physical Layer classification, the (AT True) switch will close and Opto1 will turn ON. Opto1 will pass this signal across the isolation barrier and the output collector can be connected to a controller (with a pull-up resistor connected to the controller's power rail). When Opto1 is ON the collector (output) will be Logic 0, the controller will then know that the PSE is capable of delivering 30W. To complete the protocol (and conform to the IEEE802.3 specification) the controller should then confirm that it is a Type 2 PD over the Data Link Layer\*.

If the Ag5700 detects a Single Event Physical Layer classification, Opto1 will be OFF and the output collector will be Logic 1 (via pull-up resistor). The controller should then assume that the PSE is limited to only delivering up to 15.4W.

If the PSE does not support the Physical Layer classification, Opto1 will be OFF.

The Ag5700 may operate with non-compliant IEEE802.3 POE+ PSE's.

<sup>\*</sup>There are several PSEs (including Cisco) that will only deliver ≤15.4W until they receive Type 2 PD confirmation, over the Data Link Layer.

#### **2.3 Output**

#### 2.3.1 Maximum output power

While the Ag5700 is capable of delivering a peak power output of 30W, the maximum continuous output power of the Ag5700 is 24W, this may be limited further by the available power at the input pins of the module.

A Type 2 or greater (IEEE802.3at/bt) PSE supplying Class 4 power levels shall provide a minimum of 30W at its lowest voltage of 50V from its output, however with cable, connector and rectification losses, the available power and voltage at the input pins of the Ag5700 may vary considerably. In a fully compliant IEEE802.3 system, the power available, measured at the input to the bridge rectifiers, may be as low as 25.5W. See "ANX-POE-Power" for more details.

#### 2.3.2 Output Voltage Adjust Setting

The Ag5700 has an output voltage adjustment pin, ADJ, which can be used to either increase or decrease the output voltage of the module.

**Figure 5: Output Voltage Adjustment**

| Reducing the output voltage, connect RA between ADJ and +VDC |                            |                    |  |  |  |  |  |  |

|--------------------------------------------------------------|----------------------------|--------------------|--|--|--|--|--|--|

| Value of RA Ag5712 output Ag5724 output                      |                            |                    |  |  |  |  |  |  |

| Open Circuit                                                 | 12.0V                      | 24.0V              |  |  |  |  |  |  |

| 68K Ohms                                                     | 10.8V <sup>1</sup>         | 21.6V <sup>1</sup> |  |  |  |  |  |  |

| Increasing the output vo                                     | oltage, connect RA between | ADJ and -VDC       |  |  |  |  |  |  |

| Value of RA                                                  | Ag5712 output              | Ag5724 output      |  |  |  |  |  |  |

| Open Circuit                                                 | 12.0V                      | 24.0V              |  |  |  |  |  |  |

| 0 Ohms                                                       | 12.8V                      | 24.8V              |  |  |  |  |  |  |

**Table 4: Output Voltage Adjustment Resistor Values**

Note 1: It is important that the minimum output adjust is not taken below this level. Setting the output voltage below this level may result in the module being permanently damaged.

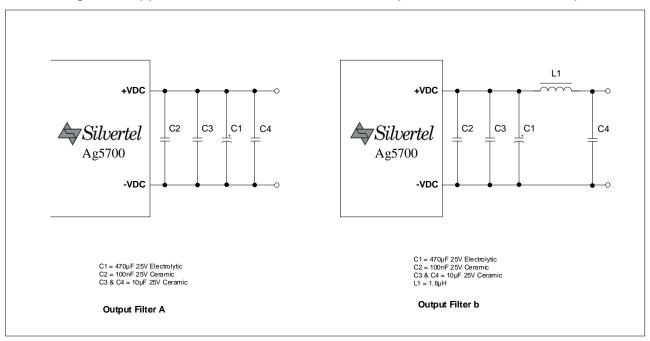

#### 2.3.3 Output Filtering

The Ag5700 only requires an electrolytic capacitor on its output for stable operation, However, greater ripple reduction can be achieved with just a few additional components.

Figure 6: Output Filter

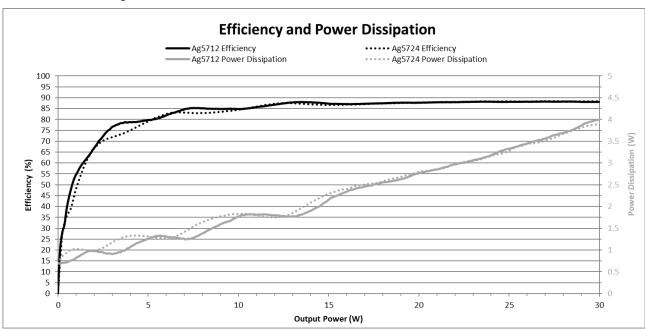

## 3 Efficiency

Figure 7: Ag5700 Efficiency

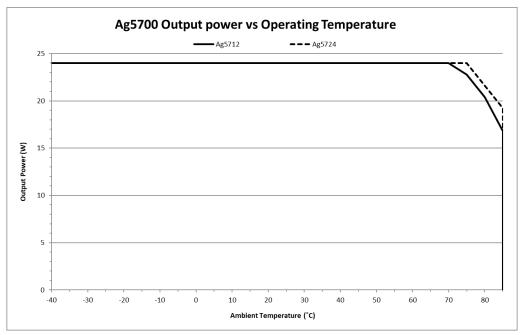

#### 4 Operating Temperature Range

At the heart of the Ag5700 is a DC/DC converter, it will generate heat. While the product has been designed with efficiency in mind, the small form factor requires that thermal management is taken into consideration at the design stage. The amount of heat generated by the module will depend on the load it is required to drive and the input voltage supplied by the PSE.

The Ag5700 can operate up to a maximum of 85°C ambient, and a minimum of -40°C ambient. When intended for used in ambient temperatures below 0°C it is recommended that an output capacitor that will retain the minimum output capacitance and ESR ratings for the Ag5700 at the lowest temperature in the intended operating range is used. A Polymer Aluminium Electrolytic Capacitor is ideal for this application, however a reputable brand rated to -55°C should suffice for most applications, please contact Silvertel if suggestions are required.

The Ag5700 is capable of a continuous output power of 24W across the operating temperature range of -40°C to +70°C, above which a derating of the continuous output power may occur.

The graphs shown are at the maximum ambient temperature under continuous load conditions which has been recorded in a Temperature Applied Sciences ECO MT135 Environmental chamber with airflow across the module at a rate of approximately 0.5m/s Operation in a sealed enclosure or with limited airflow may result in further de-rating of the operating temperature profile.

Figure 8: Ag5700 operating temperature profile

#### 4.1 Thermal Considerations

Each application is different; therefore, it is impossible to give fixed and absolute thermal recommendations. Due to the miniaturised design, it is required that a thermal interface material is used between the module and the host PCB to draw heat out and away from the module for continuous operation. It is recommended to make provision for heatsinking as follows.

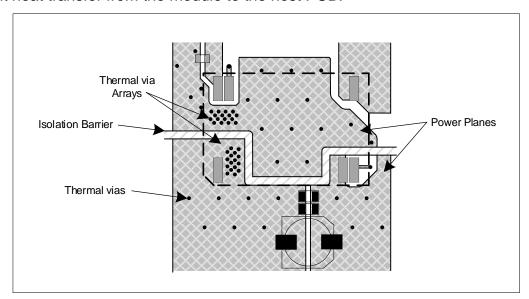

The recommended method for drawing heat away from the Ag5700 is by means of copper planes connected to the power pins of the Ag5700 along with a thermal gap filler gel fitted underneath the Ag5700, such as Parker Chomerics THERM-A-GAP GEL. This technique can be used to draw heat away from the DC/DC converter to dissipate over a larger surface area.

The copper planes must be on the outer layers of the PCB, best results are achieved with additional copper planes on internal layers of host PCB with multiple thermal via connections. An example of this is shown in Figure 9. It is also important that any enclosure has sufficient ventilation for the Ag5700.

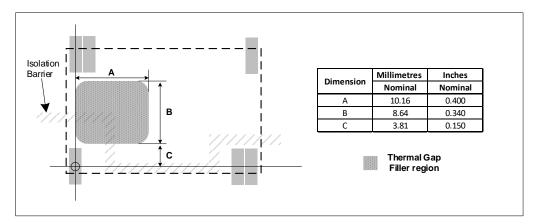

The hottest components of the Ag5700 modules are located between pins 1 and 6 on the underside of the module. It is recommended that the gap filler is applied to this region such that it encloses both the components and PCB. The gap filler can be used in combination with thermal via arrays, to reduce the thermal resistance between the copper planes. Figure 10 shows the minimum recommended application area for the gap filler to provide sufficient heat transfer from the module to the host PCB.

Figure 9: Thermal Relief

Figure 10: Thermal Interface Application Region

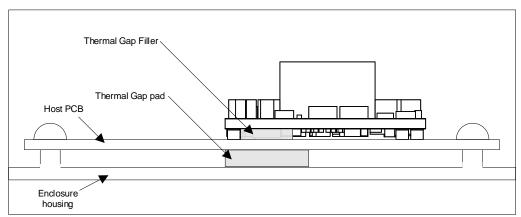

Heat dissipation can be improved further by thermally connecting to the enclosure of the application. The simplest method of performing this is to use a thermal gap pad located between the host PCB and the enclosure, situated over the area containing the thermal via arrays.

Figure 11: Additional Heatsinking

#### 5 Protection

#### 5.1 Input Protection

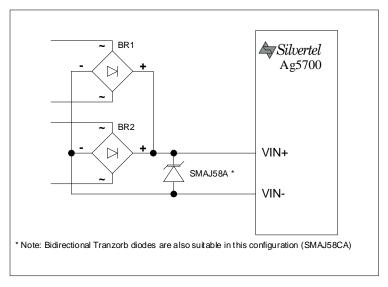

The Ag5700 may be damaged by input voltage transients greater than 80V. If protection from electrostatic discharge (ESD) or other high voltage transients is required, an overvoltage clamping device can be fitted across the VIN+ and VIN- input pins, see Figure 12 and Application Note "ANX-POE-Protection" for more details.

**Figure 12: Input Protection**

#### 5.2 Output Back Feed Protection

If an external or auxiliary supply is to be used, gating circuitry will be required, such as a blocking diode, to prevent voltage injection on to the output circuitry of the module damaging the module.

#### 5.3 Output Short Circuit Protection

The Ag5700 has over-current protection to prevent the module from becoming damaged in the event of a short circuit event. If an over current event occurs the Ag5700 will disable the output, the Aq5700 will then test the current draw approximately every 2 seconds until the cause of the over current is removed, after which, the power will be restored to the output.

#### 5.4 Thermal Protection

The Ag5700 contains built in thermal protection to prevent the module becoming damaged in the event that it is operated beyond its temperature specification. When the Ag5700 has detected it is over temperature, the output will be disabled until the module has cooled sufficiently.

#### 6 Isolation

To meet the safety isolation requirements of IEEE802.3 specification, a powered device must provide electrical isolation between all its accessible external connectors, including frame ground. In order to meet this requirement, the powered device should be subjected to and pass at least one of the following electrical strength tests of IEC 60950-1:2001 sub clause 6.2.1.

- a) 1500V<sub>rms</sub> at 50-60Hz for 60 seconds

- b) 2250V<sub>dc</sub> for 60 seconds or

- c) 1500V<sub>dc</sub> impulse test 10 times in either polarity.

To assist in this the Ag5700 has been designed to meet and pass the 1500 V<sub>dc</sub> impulse test with no breakdown of insulation.

In order to maintain this isolation requirement, it is essential that that the isolation barrier is not breached, see ANX-POE-Isolation-Barrier for more details.

#### 7 EMC

The Ag5700 has been designed to pass EN55032 Class B, however the Ag5700 will only be one component within the system so we would always advise that provisions are put in place in case further noise reductions are needed. From our experience we would recommend an inexpensive but effective solution to reduce emissions as shown in Figure 13, for more details please see ANX-POE-EMI-Considerations.

**Figure 13: Typical Connection Diagram**

## 8 Solderability

The Ag5700 has been designed with a fully automated assembly process in mind and is lead-free (Pb-free) and RoHS compliant and fully compatible with a Pb-free automated assembly process. The Ag5700 can still be mounted manually using soldering iron or hot air.

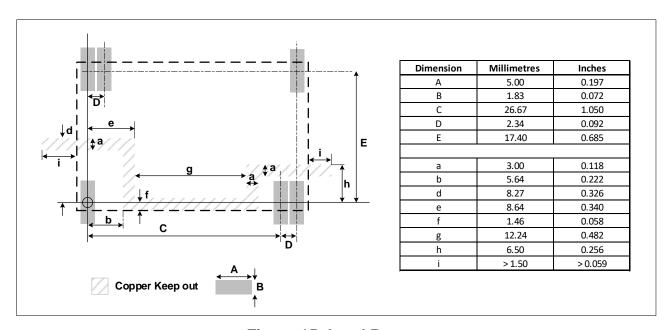

There are no specific requirements regarding stencil thickness or solder paste classification type. Solder mask defined (SMD) pads are preferred over non-solder mask defined (NSMD) pads, the land pattern dimensions are given in Figure 15.

Minimal thermal relief should be applied to the pads to allow for maximum thermal conductivity without hindering the reflow process, your Process Engineer should be able to provide suitable recommendations.

The Ag5700 requires no components of greater than Moisture Sensitivity level 1, as a result no special processes are required in the reflowing process of the Ag5700.

Note: Do not pass the Ag5700 through the reflow process mounted to the underside of the assembly due to the risk of components falling off the module.

#### 8.1 Solder Profile

Below is a typical profile that the Ag5700 should be mounted, based on the J-STD-020 standard for Pb-Free applications. Exceeding these specifications may cause damage to the module. All production environments are different therefore please review these guidelines with the process engineer prior to use.

|               | Zone 1 | Zone 2 | Zone 3 | Zone 4 | Zone 5 | Units                  |

|---------------|--------|--------|--------|--------|--------|------------------------|

| Zone Duration | 42     | 42     | 42     | 42     | 42     | Seconds                |

| Top Heater    | 150    | 180    | 210    | 240    | 270    | °C                     |

| Bottom Heater | 150    | 180    | 210    | 240    | 270    | °C                     |

| Typical Slope | 2.1    | 1.2    | 1.1    | 0.9    | 0.8    | °C/Second              |

| Airflow rate  | 40     |        |        |        |        | M <sup>3</sup> /Minute |

**Table 5: Solder Profile**

|                            | Min | Max | Units     |

|----------------------------|-----|-----|-----------|

| Soak Time (s)<br>150-180°C | 30  | 90  | Seconds   |

| Time above (s)<br>≥220°C   | 30  | 90  | Seconds   |

| Peak Temperature (°C)      | 230 | 255 | ,C        |

| ΔTemperature (°C/s)        | -3  | 3   | °C/Second |

**Table 6: Solder Parameters**

#### 9 Electrical Characteristics

## 9.1 Absolute Maximum Ratings

|   | Parameter                  | Symbol | Min  | Max  | Units |

|---|----------------------------|--------|------|------|-------|

| 1 | DC Supply Voltage          | Vcc    | -0.3 | 60   | V     |

| 2 | Storage Temperature        | Ts     | -40  | +100 | °C    |

| 3 | Moisture Sensitivity Level | MSL    | -    | 1    | -     |

Note: Exceeding the above ratings may cause permanent damage to the product. Functional operation under these conditions is not implied. Maximum ratings assume free airflow.

#### 9.2 Recommended Operating Conditions

|   | Parar                            | Symbol            | Min    | Тур | Max | Units         |         |

|---|----------------------------------|-------------------|--------|-----|-----|---------------|---------|

| 1 | Supply                           | VIN               | 40     | 52  | 57  | V             |         |

| 2 | Transient Su                     | V <sub>TRAN</sub> | 36     |     |     | V             |         |

| 3 | Input Under Voltage Lockout      |                   | Vulock | 30  |     | 36            | V       |

| 4 | Operating Temperature            |                   | TOP    | -40 | 25  | 85            | Ta / °C |

| 5 | Output Ag5712 capacitance Ag5724 | Ag5712            | Cout   | 220 | 470 | 1000          | μF      |

|   |                                  | capacitance       | 220    | 330 | 470 | <b>I</b> -: • |         |

Note 1: For transient events lasting between 30µs to 250µs, as detailed in the IEEE802.3 specification

#### 9.3 DC Electrical Characteristics

|   | DC Characteristic                |              | Sym                | Min   | Typ <sup>1</sup> | Max  | Units             | Comments            |

|---|----------------------------------|--------------|--------------------|-------|------------------|------|-------------------|---------------------|

| 1 | Nominal<br>Output                | Ag5712       | +Vout              | 11.5  | 12               | 12.5 | V                 |                     |

| - | Voltage                          | Ag5724       | 1 001              | 23.25 | 24               | 24.8 | -                 |                     |

| 2 | Continuous<br>Current            | Ag5712       | LOAD               |       |                  | 2    | Α                 |                     |

| _ | output <sup>2</sup>              | Ag5724       | ILOAD              |       |                  | 1    | A                 |                     |

| 3 | Line Regulation                  |              | V <sub>LINE1</sub> |       | 0.1              |      | %                 | @ 50% load          |

| 4 | Load Regulation                  |              | VLOAD1             |       | 0.2              |      | %                 | @ 57V <sub>in</sub> |

| 5 | Ripple and<br>Noise <sup>3</sup> | Ag5712       | V <sub>RN</sub>    |       | 124              |      | mV <sub>p-p</sub> | At Full Load        |

| 5 |                                  | Ag5724       |                    |       | 99               |      |                   | At Full Load        |

| 6 | Minimum Load                     |              | Imin               | 0     |                  |      | mA                |                     |

| 7 | Short-Circu                      | it Duration  | T <sub>SC</sub>    |       |                  | 8    | sec               |                     |

| 8 | Peak<br>Efficiency <sup>2</sup>  | Ag5712       |                    |       | 88.4             |      | 0/                |                     |

| 8 |                                  | Ag5724       | EFF                |       | 88.6             |      | %                 |                     |

| 9 | Isolation Vo                     | oltage (I/O) | Viso               |       |                  | 1500 | V <sub>PK</sub>   | Impulse Test        |

Note 1: Typical figures are at 25°C with a nominal output voltage with 57V supply with a 470µF output capacitor fitted and are for design aid only. Not Guaranteed.

Note 2: Minimum 42.5 $V_{in}$  for maximum output at 25 $^{\circ}$ C. Maximum output power may be limited by PSE.

Note 3: Measured with external filter A. The output ripple and noise can be reduced further with external filter B, see Section 2.3.3.

## 10 Package

**Figure 14: Package Dimensions**

Figure 15: Land Pattern

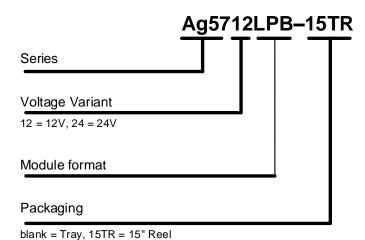

## 11 Ordering Code

## 12 Packaging

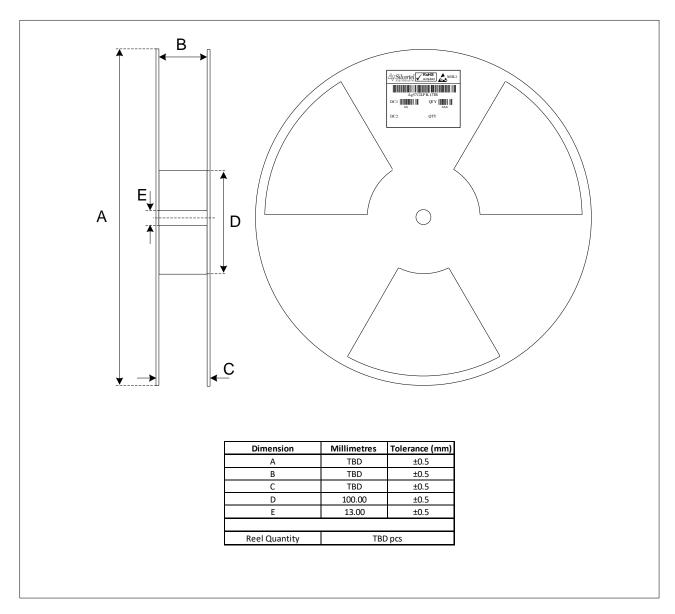

The default packing for the Ag5700LPB series is supplied in trays of 72, additionally there is the option for the Ag5700LPB to be packaged on a 13 inch reel.

**Figure 16: Tape Dimensions**

Figure 17: Reel Dimensions

Information published in this datasheet is believed to be correct and accurate. Silver Telecom assumes no liability for errors which may occur or for liability otherwise arising out of use of this information or infringement of patents which may occur as a result of such use. No license is granted by this document under patents owned by Silver Telecom or licensed from third parties by Silver Telecom. The products, their specification and information appearing in this document are subject to change by Silver Telecom without notice.