KDS Quarzoszillatoren für 156,25MHz- und 312,5MHz-Anwendungen

High Speed-Kommunikation braucht präziseres Timing

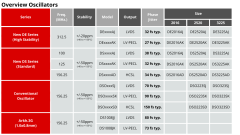

Der Datenverkehr wächst rasant, beschleunigt durch KI-basierte Anwendungen. Optische Standards entwickeln sich von 400G zu 800G, 1,6T ist bereits absehbar, parallel steigt PCIe auf Gen 6.0. Diese Entwicklungen erhöhen die Anforderungen an Timing-Komponenten erheblich. High-Speed-Systeme mit PAM4 benötigen Oszillatoren mit hoher Frequenz, extrem niedrigem Jitter und enger Frequenzstabilität. Daishinku Corporation (KDS) bietet dafür die neuen differenziellen Serien DS und DE.

DS-Serie – Neuer Standard für gängige Frequenzen

Die DS-Serie richtet sich an gängige Frequenzen wie 156,25MHz und bietet deutlich verbesserte Jitter-Eigenschaften. Während bisherige Lösungen etwa 90fs typischen Jitter aufweisen, erreicht der neue DS2520AK nur 32fs typisch, was für deutlich höhere Signalintegrität in High-Speed-Systemen sorgt.

Wesentliche Merkmale der DS-Serie

- Frequenzen: 100MHz, 125MHz, 156,25MHz

- Frequenzabweichung: ±50 ppm (-40°C bis +105°C)

- Ausgangsstandards: LV-PECL, LVDS, HCSL

- Baugrößen: 2,0×1,6mm und 2,5×2,0mm

- Muster sind bereits verfügbar. Die Massenproduktion startet im Juni 2026.

DE-Serie – Höhere Präzision und 312,5 MHz Unterstützung

Die DE-Serie erweitert die Leistungsfähigkeit durch eine engere Frequenzstabilität (±20 ppm) und unterstützt höhere Frequenzen bis 312,5MHz. Damit eignet sie sich besonders für kommende High-Speed-Schnittstellen.

Wesentliche Merkmale der DE-Serie

- Frequenzen: 100MHz, 125MHz, 156,25MHz, 312,5MHz

- Frequenzabweichung: ±20 ppm (-40°C bis +105°C)

- Ausgangsstandards: LV-PECL und LVDS (HCSL folgt)

- Baugrößen: 2,0×1,6mm und 2,5×2,0mm

- Muster sind bereits verfügbar. Die Massenproduktion startet im August 2026.

Warum sind Quarzoszillatoren mit extrem niedrigem Jitter für High-Speed-Kommunikation (zB PAM4, 800G oder PCIe Gen6) so wichtig?

Bei modernen Hochgeschwindigkeits-Schnittstellen wie 800G-Optik, 1.6T-Netzwerken oder PCIe Gen6 werden häufig PAM4-Modulationsverfahren eingesetzt, um höhere Datenraten zu erreichen. Diese Technik macht das Signal jedoch deutlich empfindlicher gegenüber Timing-Fehlern.

Der wichtigste Parameter für Timing-Bausteine ist deshalb Jitter. Bereits kleinste Jitter-Abweichungen können zu Bitfehlern, Datenverlust oder Synchronisationsproblemen zwischen Transceivern führen.

Dank ihres hohen Q-Faktors erreichen quarzbasierte Oszillatoren deutlich geringere Jitterwerte als MEMS-Lösungen, die intern Frequenzmultiplikation verwenden. Daher sind Low-Jitter-Quarzoszillatoren eine Schlüsselkomponente für die nächste Generation von High-Speed-Netzwerken, Rechenzentren und AI-Infrastruktur.

Oszillatorarchitektur

Beide Serien basieren auf der Arkh.2G-Oszillatorarchitektur von KDS, die eine mehrlagige Quarzstruktur („Arkh.3G“) nutzt. Diese Technologie verbessert Schockresistenz, Zuverlässigkeit und Produktionsskalierbarkeit und ermöglicht gleichzeitig ultrakompakte Oszillatoren bis 1,0×0,8mm.

Vorteile von Quarzoszillatoren mit differenziellem Ausgang

- Extrem niedriger Jitter für stabile Hochgeschwindigkeitssignale

- Hohe Frequenzen wie 156,25MHz oder 312,5MHz, die häufig in Netzwerk- und SerDes-Architekturen verwendet werden

- Hohe Störfestigkeit für PAM4-Signale

- Präzise Frequenzstabilität für zuverlässige Synchronisation

Ihr Ansprechpartner

Wenn Sie ultrakompakte Oszillatoren benötigen, wenden Sie sich an Yasunobu Ikuno.